Ao9

37

Michele Angelaccio / Berta Buttarazzi

# Reti logiche

PARTE SECONDA

*Reti sequenziali*

Copyright © MMIV

ARACNE EDITRICE S.r.l.

[www.aracneeditrice.it](http://www.aracneeditrice.it)

[info@aracneeditrice.it](mailto:info@aracneeditrice.it)

00173 Roma

via Raffaele Garofalo, 133 A/B

(06) 93781065

ISBN 88-7999-663-0

*I diritti di traduzione, di memorizzazione elettronica,

di riproduzione e di adattamento anche parziale,

con qualsiasi mezzo, sono riservati per tutti i Paesi.*

I edizione: febbraio 2004

## Sommario

|                                                              |    |

|--------------------------------------------------------------|----|

| 1 Introduzione.....                                          | 2  |

| 2 Circuiti booleani con ciclo.....                           | 4  |

| 2.1 Porte Con Ciclo.....                                     | 6  |

| 2.2 Circuiti Bistabili.....                                  | 10 |

| 2.3 Domande.....                                             | 16 |

| 3 Automi a Stati Finiti.....                                 | 17 |

| 3.1 Preliminari.....                                         | 17 |

| 3.2 ASF e Reti Sequentziali.....                             | 23 |

| 3.3 Riduzione del numero degli stati.....                    | 29 |

| 3.4 Domande.....                                             | 36 |

| 3.5 Problemi.....                                            | 38 |

| 4 La Realizzazione di Reti Sequentziali.....                 | 41 |

| 4.1 Reti Sequentziali Sincrone.....                          | 41 |

| 4.2 Elementi di Memoria.....                                 | 45 |

| 4.2.1II latch S-R.....                                       | 46 |

| 4.2.2II latch D.....                                         | 47 |

| 4.2.3II flip-flop D.....                                     | 48 |

| 4.2.4II flip-flop JK.....                                    | 51 |

| 4.3 Sintesi di Reti Sequentziali Sincrone con Flip-Flop..... | 53 |

| 4.3.1 Sintesi con Flip-Flop D.....                           | 54 |

| 4.3.2 Sintesi con Flip-Flop SR o JK.....                     | 57 |

| 4.4 Analisi di Reti Sequentziali Sincrone.....               | 61 |

| 4.5 Domande.....                                             | 63 |

| 4.6 Problemi.....                                            | 64 |

| 5 Reti Sequentziali Standard.....                            | 69 |

| 5.1 Registri.....                                            | 69 |

| 5.2 Contatori.....                                           | 72 |

| 6 Bibliografia.....                                          | 75 |

# 1 Introduzione

Le Reti Sequentziali sono sistemi caratterizzati dal fatto che il loro comportamento in un generico istante  $t$  non dipende solo dal valore degli ingressi, come nelle reti combinatorie, ma anche dallo stato interno della rete logica. Lo stato rappresenta una condizione in cui il sistema si trova tenendo conto degli input ricevuti in precedenza e da esso dipende il comportamento del sistema a fronte di input successivi.

Per studiare tali sistemi, vista la loro diversità di funzionamento, è necessario un modello di calcolo, detto sequenziale, più complesso e con l'obiettivo di memorizzare, attraverso il concetto di stato interno della rete logica, la sequenza degli ingressi precedenti.

Numerosi sono i problemi che richiedono questa tipologia di reti per calcolare le uscite. Ad esempio consideriamo la somma  $n$ -bit e supponiamo che l'ingresso dei dati alla rete sia sequenziale invece che parallelo. In questo caso gli ingressi sono solo tre: un bit per ogni operando e uno per il riporto e l'output del circuito deve essere calcolato tenendo conto che i dati arrivano in modo sequenziale.

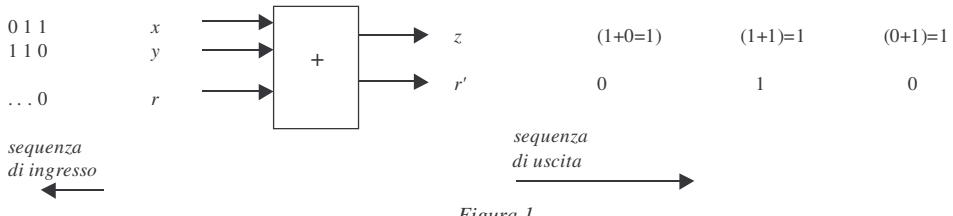

E' facile osservare che in questo caso il circuito combinatorio precedentemente analizzato per l'addizionatore 1-bit non è in grado di calcolare il risultato corretto. Infatti come riportato in Figura 1 , il risultato che viene prodotto in sequenza nell'output  $z$  è 111 con riporto finale 0 e non 001 con riporto finale 1, in quanto il circuito combinatorio calcola singoli bit di somma e riporto.

Figura 1

Per ottenere il risultato corretto è necessaria la memoria del valore di riporto calcolato al passo precedente. Questo obiettivo può essere ottenuto semplicemente con un collegamento in feedback della linea di riporto, ma in questo caso il circuito risultante non soddisfa più la definizione di grafo aciclico, pertanto non può essere considerato una rete combinatoria.

Queste tipologie di circuiti ciclici sono detti anche reti logiche sequenziali (RLS) e saranno oggetto di studio in questo capitolo. Inizieremo a trattare la nozione di circuito booleano con

ciclo mediante equazioni booleane nel tempo o ricorrenti e vedremo il caso di una porta con ciclo e quello di due porte NOR con ciclo. Quest'ultimo costituisce l'elemento di base per la progettazione di RLS più complesse. Successivamente analizzeremo il modello algebrico di automa che si dimostra esattamente equivalente alla semantica di un circuito booleano con ciclo.